便攜式多功能數字分析儀的前放電路設計——集成電路設計視角

便攜式多功能數字分析儀集信號采集、處理與分析于一身,廣泛用于工業檢測、環境監測及科研實驗等領域。其性能的核心之一在于前端放大電路(前放電路),它直接決定了儀器對微弱信號的拾取能力、信噪比及動態范圍。從集成電路(IC)設計的角度出發,設計一款高性能、低功耗、高集成度的前放電路,是實現儀器便攜化與多功能化的關鍵。

一、 設計需求與挑戰

便攜式設備的前放電路設計需兼顧多項苛刻指標:

- 低噪聲:需精確放大微伏級甚至納伏級微弱信號,要求等效輸入噪聲電壓密度極低,通常在nV/√Hz量級。

- 高輸入阻抗:減少對被測信號源的負載效應,尤其在連接高阻抗傳感器時至關重要。

- 低功耗:延長電池續航,要求電路在滿足性能的前提下,工作電流盡可能小。

- 高共模抑制比(CMRR)與電源抑制比(PSRR):有效抑制環境共模干擾與電源波動,提升測量精度。

- 寬動態范圍與可編程增益:適應不同幅值的輸入信號,需集成可編程增益放大器(PGA)。

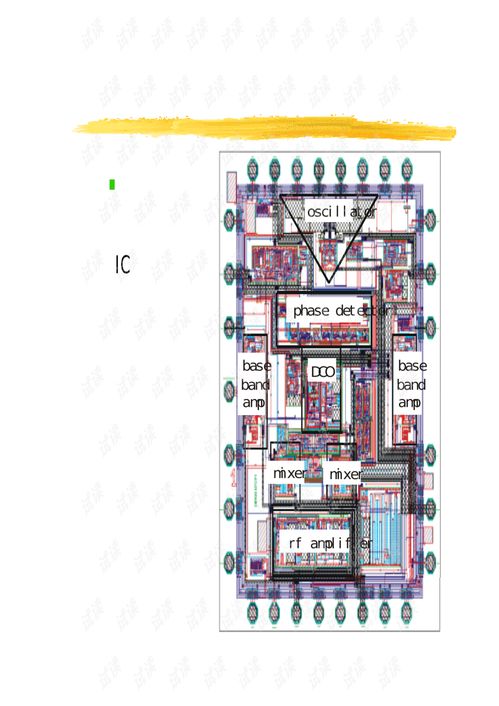

- 小型化與高集成度:通過IC設計將多級放大器、濾波、偏置等電路集成于單顆芯片,減少外圍元件,縮小體積。

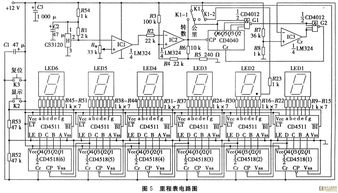

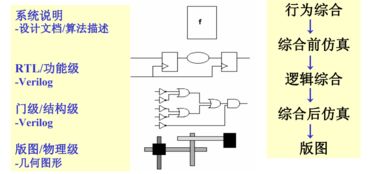

二、 集成電路架構設計

典型的集成化前放電路可采用以下架構:

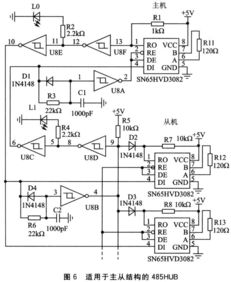

- 儀表放大器(IA)核心:作為第一級,采用三運放或自穩零架構的集成儀表放大器,提供高輸入阻抗、高CMRR及精確的差分放大。IC設計需優化內部匹配電阻網絡,以獲取高共模抑制和增益精度。

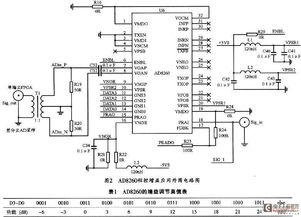

- 可編程增益級(PGA):緊隨IA之后,通過開關電容網絡或精密的模擬開關切換反饋電阻,實現多檔位增益控制。數字接口(如SPI)集成于芯片內,便于微處理器控制。

- 濾波與驅動:集成抗混疊低通濾波器(可編程截止頻率),并設計輸出緩沖級以驅動后續ADC。

- 基準與偏置:芯片內部集成高穩定性帶隙基準電壓源與低噪聲偏置電路,確保各級工作點穩定,降低對外部元件的依賴。

三、 關鍵IC設計技術

- 低噪聲設計:選用低噪聲的CMOS或BiCMOS工藝。在電路層面,輸入級采用長溝道晶體管增大面積以降低1/f噪聲;優化偏置電流,在功耗與熱噪聲間取得平衡;采用相關雙采樣(CDS)或斬波穩零(Chopper)技術,進一步抑制低頻噪聲與失調。

- 低功耗設計:采用亞閾值設計技術,使部分晶體管工作在亞閾值區,大幅降低靜態電流;設計多電源域,對非關鍵路徑進行動態電源管理;優化運放的擺率與帶寬,滿足信號保真度的同時最小化功耗。

- 高精度匹配設計:利用工藝的匹配特性,采用共質心、交叉耦合等版圖技術,精心設計差分對與電阻陣列,確保增益精度和CMRR。

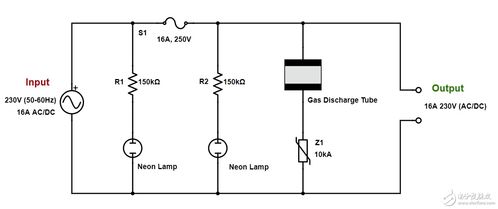

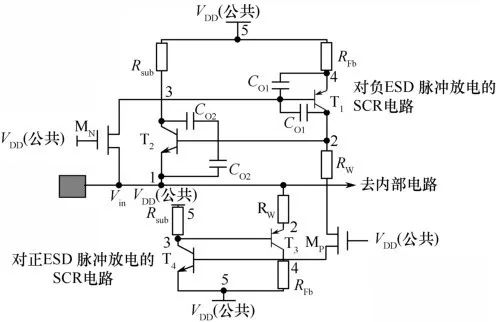

- 電源與抗干擾設計:在芯片內部增加去耦電容與穩壓電路,提高PSRR;采用屏蔽、隔離環等版圖技術,減少襯底噪聲耦合與串擾。

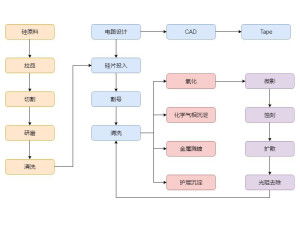

四、 系統集成與測試考量

完整的IC設計需包含與后端數字處理器的接口(如數字控制邏輯、狀態寄存器)。芯片在流片后,需進行嚴格的測試,包括噪聲譜密度測量、增益誤差、非線性度、CMRR/PSRR測試以及全溫度范圍內的性能驗證。

結論:從集成電路視角設計便攜式數字分析儀的前放電路,是一個系統工程,需在工藝選擇、電路架構、版圖實現與系統集成等多個層面進行深度優化。通過高度集成的IC方案,能夠實現前放電路在性能、功耗、體積和可靠性上的最佳平衡,從而為便攜式多功能數字分析儀提供強大的“感官”核心,推動其在更廣泛領域的應用。

如若轉載,請注明出處:http://www.amwayp.cn/product/78.html

更新時間:2026-03-31 09:24:36